優化乘加器并行計算的軟件設計與開發策略

在現代計算系統中,乘加器(Multiply-Accumulate, MAC)是許多高性能應用(如數字信號處理、機器學習和科學計算)的核心組件。為了充分發揮硬件潛力,軟件設計和開發必須針對乘加器的并行計算進行優化。以下是一些關鍵策略:

- 算法層面的并行化設計:

- 選擇支持數據并行或任務并行的算法,例如將矩陣乘法分解為多個獨立的子任務。

- 利用分治策略,將大問題拆分為可并行處理的小塊,減少乘加器間的依賴。

- 利用現代編程模型和框架:

- 采用OpenMP、CUDA或OpenCL等多線程或GPU編程模型,直接控制乘加器單元的并行執行。

- 使用高度優化的庫,如Intel MKL或NVIDIA cuBLAS,它們內置了對乘加器并行計算的優化。

- 數據布局與內存訪問優化:

- 設計數據結構和內存布局以減少緩存未命中和內存帶寬瓶頸,例如使用連續內存塊和對齊數據。

- 實現數據預取和流水線技術,確保乘加器單元持續工作,避免空閑等待。

- 負載均衡與任務調度:

- 在軟件中動態分配任務,確保所有乘加器單元均勻負載,避免部分單元過載而其他空閑。

- 使用線程池或工作隊列機制,根據系統資源自動調整并行度。

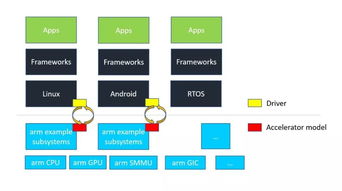

- 硬件特性適配與編譯器優化:

- 針對特定硬件架構(如SIMD指令集)進行代碼優化,例如使用AVX或NEON指令顯式并行化乘加操作。

- 利用編譯器標志(如-O3、-ffast-math)自動向量化代碼,提升乘加器并行效率。

- 性能分析與調試:

- 使用性能分析工具(如gprof、VTune或Nsight)識別并行計算中的瓶頸,例如乘加器利用率低或同步開銷過大。

- 實施迭代優化,根據分析結果調整軟件設計,例如減少鎖競爭或改進數據局部性。

高效并行乘加器計算需要軟件設計與開發的全面考慮,從算法選擇到硬件適配,再到持續的性能調優。通過這些策略,開發人員可以最大化計算吞吐量,滿足高性能應用的需求。

如若轉載,請注明出處:http://www.0451job.cn/product/22.html

更新時間:2026-02-23 10:12:58